- 您现在的位置:买卖IC网 > Sheet目录479 > MRF49XAT-I/ST (Microchip Technology)IC RF TXRX 433/868/915 16-TSSOP

�� �

�

�

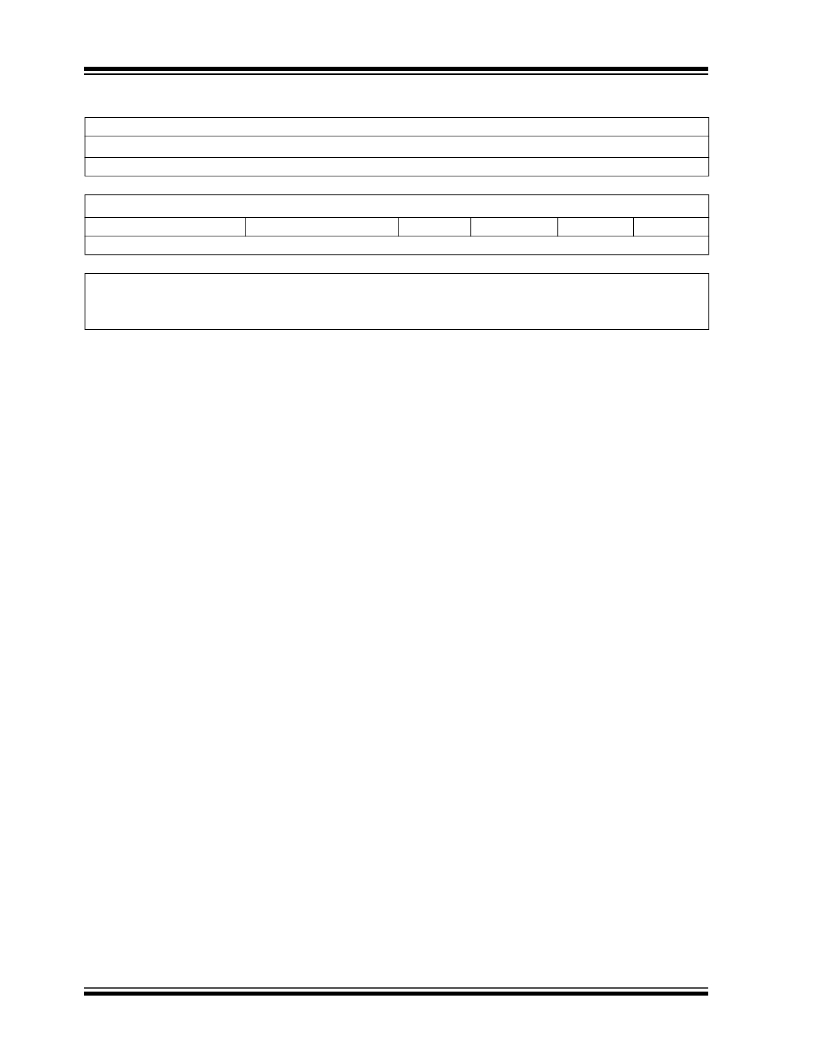

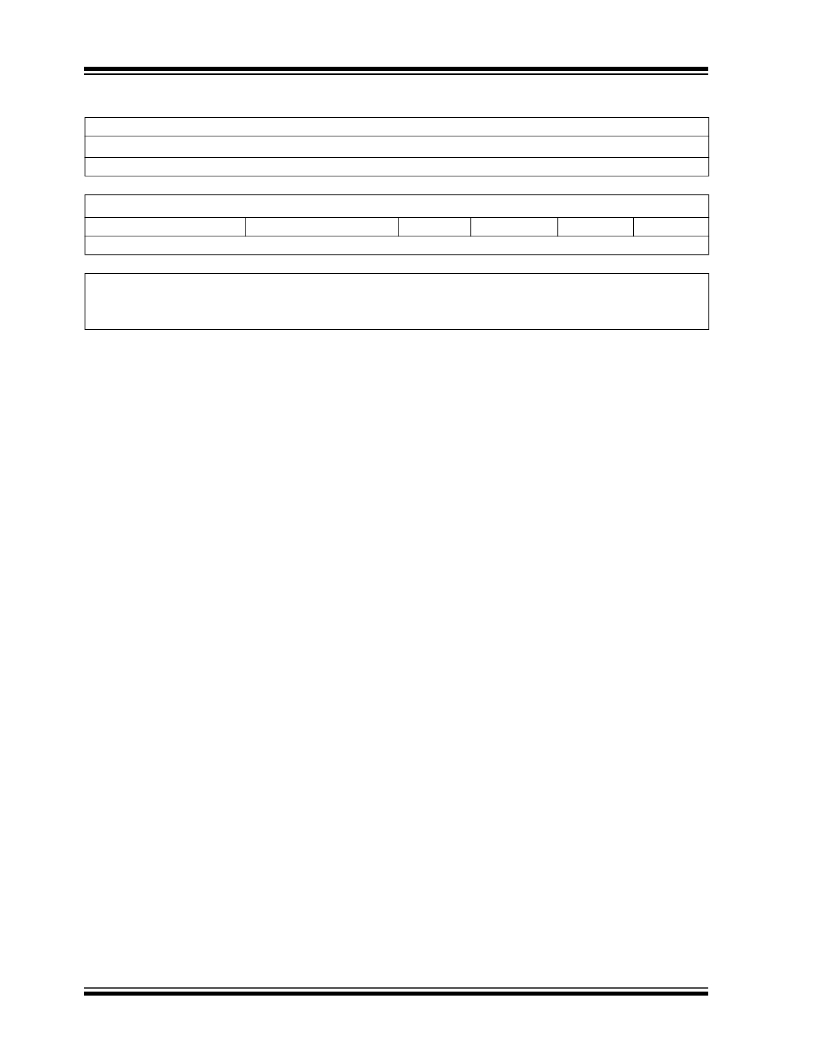

�MRF49XA�

�REGISTER� 2-3:�

�AFCCREG:� AUTOMATIC� FREQUENCY� CONTROL� CONFIGURATION� REGISTER�

�(POR:� 0xC4F7)�

�W-1�

�W-1�

�W-0�

�W-0�

�W-0�

�W-1�

�W-0�

�W-0�

�CCB<15:8>�

�bit� 15�

�bit� 8�

�W-1�

�W-1�

�W-1�

�W-1�

�W-0�

�W-1�

�W-1�

�W-1�

�AUTOMS<1:0>�

�ARFO<1:0>�

�MFCS�

�HAM�

�FOREN�

�FOFEN�

�bit� 7�

�Legend:�

�r� =� reserved� bit�

�bit� 0�

�R� =� Readable� bit�

�W� =� Writable� bit�

�U� =� Unimplemented� bit,� read� as� ‘0’�

�-n� =� Value� at� POR�

�‘1’� =� Bit� is� set�

�‘0’� =� Bit� is� cleared�

�x� =� Bit� is� unknown�

�bit� 15-8�

�bit� 7-6�

�bit� 5-4�

�bit� 3�

�bit� 2�

�bit� 1�

�bit� 0�

�Note� 1:�

�2:�

�3:�

�CCB<15:8>:� Command� Code� bits�

�The� command� code� bits� (� 11000100b� )� are� serially� sent� to� the� microcontroller� to� identify� the� bits� to� be�

�written� in� the� AFCCREG.�

�AUTOMS<1:0>:� Automatic� mode� Selection� bits� (for� AFC)�

�These� bits� select� the� operation� type� (automatic/manual)� for� performing� AFC� based� on� the� status� of�

�the� MFCS� bit.�

�11� =� Keeps� offset� independent� for� the� state� of� the� DIO� signal�

�10� =� Keeps� offset� only� while� receiving� (DIO� =� High)�

�01� =� Runs� and� measures� only� once� after� each� power-up� cycle�

�00� =� Auto� mode� off� (controlled� by� microcontroller)�

�ARFO<1:0>:� Allowable� Range� for� Frequency� Offset� bits�

�These� bits� select� the� offset� range� allowable� between� transmitter� and� receiver� frequencies.�

�11� =� +3� F� RES� to� -4� F� RES� (1)�

�10� =� +7� F� RES� to� -8� F� RES�

�01� =� +15� F� RES� to� -16� F� RES�

�00� =� No� restriction�

�MFCS:� Manual� Frequency� Control� Strobe� bit�

�This� bit� is� the� strobe� signal� which� initiates� the� manual� frequency� control� sample� to� calculate� the� offset� error.�

�1� =� A� sample� of� a� received� signal� is� compared� with� a� receiver� Local� Oscillator� (LO)� signal� and� an� offset�

�error� is� calculated.� If� bit� 1� is� enabled,� the� value� is� stored� in� the� Offset� register� of� the� AFC� block.� (2)�

�0� =� Ready� for� the� next� sample�

�HAM:� High-Accuracy� (Fine)� mode� bit� (3)�

�1� =� Switches� the� Frequency� Control� mode� to� High-Accuracy� mode�

�0� =� Frequency� Control� mode� works� in� regular� mode�

�FOREN:� Frequency� Offset� Register� Enable� bit�

�1� =� Enables� the� offset� value� calculated� by� the� offset� sample.� The� offset� value� is� added� to� the� frequency�

�control� word� of� the� PLL� which� tunes� the� desired� carrier� frequency.�

�0� =� Denies� the� addition� of� the� offset� value� to� the� frequency� control� word� of� the� PLL�

�FOFEN:� Frequency� Offset� Enable� bit�

�1� =� Enables� the� frequency� offset� calculation� using� the� AFC� circuit�

�0� =� Disables� the� frequency� offset� calculation� using� the� AFC� circuit�

�The� F� RES� is� the� frequency� tuning� resolution� for� each� band.� The� F� RES� for� each� band� is� as� follows:�

�433� MHz� =� 2.5� kHz�

�868� MHz� =� 5� kHz�

�915� MHz� =� 7.5� kHz�

�The� offset� error� value� is� stored� in� the� Offset� register� (FOREN� bit� should� be� enabled)� in� the� AFC� block� and�

�is� added� to� the� frequency� control� word� of� the� PLL.� Reset� this� bit� before� initiating� another� sample.�

�In� High-Accuracy� (Fine)� mode,� the� processing� time� is� twice� the� regular� mode,� but� the� uncertainty� of� the�

�measurement� is� significantly� reduced.�

�DS70590C-page� 22�

�Preliminary�

�?� 2009-2011� Microchip� Technology� Inc.�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XA-I/MQ

TXRX ISM SUB-GHZ ULP 32QFN

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF49XAT-I/T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF4A(AMMO)

制造商:Bel Fuse 功能描述:FUSE

MRF5

制造商:Ferraz Shawmut 功能描述:

MRF50

制造商:Ferraz Shawmut 功能描述:

MRF500

制造商:Ferraz Shawmut 功能描述:

MRF5003

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:N-CHANNEL BROADBAND RF POWER FET